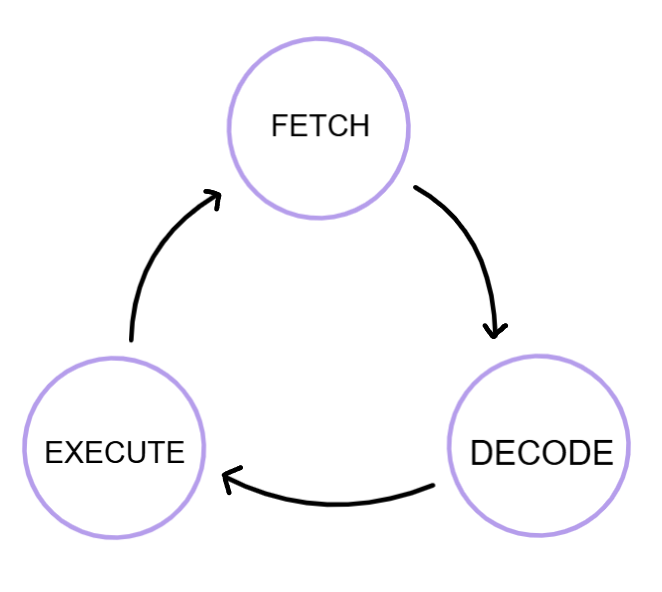

Stage 1: Fetch

Stage 1: Fetch- Program Counter (PC) holds the address of the next instruction.

- The address is copied to the Memory Address Register (MAR).

- A read signal is sent via the Control Bus to memory.

- The instruction at that address is fetched and placed in the Memory Data Register (MDR).

- The instruction is then copied into the Current Instruction Register (CIR).

- The PC is incremented to point to the next instruction.

Purpose: To retrieve the next instruction from memory so the CPU knows what to do next.

Stage 2: Decode

- The Control Unit (CU) reads the instruction from the CIR.

- It interprets the opcode (operation code) and identifies what needs to be done.

- If the instruction involves data, the CU may fetch it from memory or registers.

Purpose: To understand the instruction and prepare the CPU to carry it out.

Stage 3: Execute

- The Arithmetic Logic Unit (ALU) performs operations like addition, subtraction, or logic comparisons.

- The Accumulator (ACC) stores the result of the operation.

- If the instruction involves moving data, it is transferred between registers or memory.

- The Control Unit may update flags or change the flow of execution (e.g., branching).

Purpose: To perform the actual task the instruction specifies.

Cycle Continuation

After execution, the cycle returns to the fetch stage, using the updated Program Counter. This loop continues until the program ends or the CPU is halted.